## mmWave 5G and Radar

## 應用於第五代行動通訊和雷達感測之毫米波本地振盪器 與鎖相迴路設計分享 (mmW LO and PLL for 5G and Radar Sensor)

**社群網**址

深耕計畫 – 毫米波5G通訊及雷達感測社群活動

主持人:臺北大學 電機工程學系 郭岳芳 博士(第22屆系友)

時間: 108.9.26 (四)19:00-21:00

地點: SF738

餐點: PIZZA and Drink

經費來源: 深耕計畫

計畫召集人: 林昇洲 主任

## 學歷: 國立東華大學 電機工程學研究所

簡述: 10 years experience developing radio frequency integrated circuits in CMOS technology included local oscillator, frequency synthesizers, and clock generator. Three year experience of working is in the areas of millimeter astronomical oscillators and astronomical instrumentation design, yield phase-locked broadband VCO and YIG-tuned oscillator module for astronomical heterodyne receiver applications.

現職: Assistant Professor, National Taipei University, Dept. of EE, Sep. 2015 - present

經歷: Academia Sinica Institute of Astronomy and Astrophysics (中央研究院天文及天文物理研究所) Post doc Fellow, Sep. 2010 - Sept. 2015; Engineer Staff, Sep. 2008 - Aug. 2010

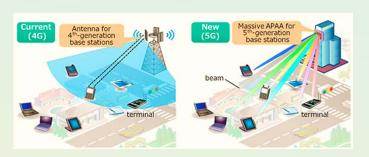

由於第五代行動通訊(5G)系統與雷達感測系統(Radar Sensor)的發展與應用日趨重要,本地振盪訊號 (LO)頻率逐漸由sub-6GHz頻率朝毫米波(mmW)頻帶邁進,因此mmW LO設計顯得格外重要。

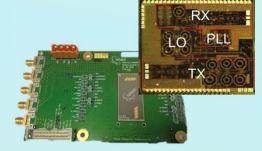

- ▶ LO主要由鎖相迴路(Phase-locked Loops, PLL)架構所組成,利用低雜訊晶體振盪器的低頻率訊(REF) ,經由PLL內的除頻器(N),倍頻至高頻率訊號,若要支援多頻帶切換頻率的需求,除頻器需要支援 多除數的切換,此PLL架構又稱之為頻率合成器,也就是目前所使用的LO訊號。

- ▶ 現今市售頻率合成器晶片規格,皆以壓控振盪器(VCO)產生核心基頻,再利用內建倍頻電路將頻率 加倍至Ku-band(12-18GHz),若要符合5GNR的28GHz頻帶,則再需要外接倍頻器將頻率提升至Kaband(27-40GHz)的RF頻帶。

- ▶ 市售PLL晶片除了提供模組驗證外,還提供免費軟體工具給使用者驗證不同核心VCO的相位雜訊效 能與系統穩定度分析。

## 本次演講主題主要分為幾個重點:

- PLL原理與系統穩定度介紹

- mmW PLL的電路架構與方塊圖

- 現今PLL產品介紹與功能解說

- LO訊號的相位雜訊介紹與分析