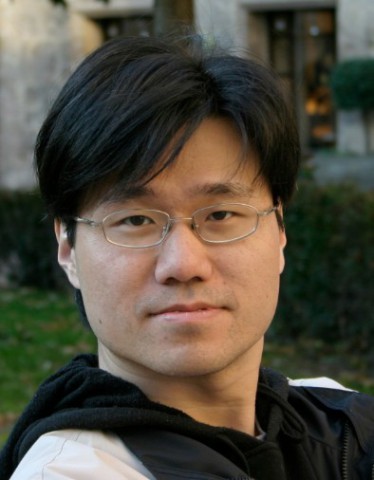

盛鐸

2017/07/10

| Email: | [email protected] |

| phone: | 02-29053800 |

| phone2: | :02-29052423(chairman line) |

| office/research room: | SF707 |

| education: | Ph.D., Electronics Engineering, National Chiao Tung University |

| expertise: | Digital IC Design, All-Digital Clock Generator Design, and Biomedical IC Design |

Educations:

2010/6: Ph.D., Electronics Engineering, National Chiao Tung University

1999/6: M.S., Electrical Engineering, National Chung Cheng University

1997/6: B.S., Electrical Engineering, National Chung Cheng University

Professional Experience:

2022/08 ~ Present: Professor and Chairman, Department of Electrical Engineering, Fu Jen Catholic University

2016/02 ~ 2022/07: Associate Professor, Department of Electrical Engineering, Fu Jen Catholic University

2010/09 ~ 2016/01: Assistant Professor, Department of Electrical Engineering, Fu Jen Catholic University

2010/03 ~ 2010/07: Senior Engineer, Sunplus(凌陽科技)

2007/01 ~ 2009/09: Project Manager, KeyASIC(佳易科技)

1999/10 ~ 2006/12: Consultant Engineer, Macronix(旺宏電子)

Research Interests:

Low-Power and System-on-a-Chip (SoC) Design Technology

All-Digital Clock Generator Design

High-Speed Serial Link Interface

Biomedical IC Design

Laboratory:

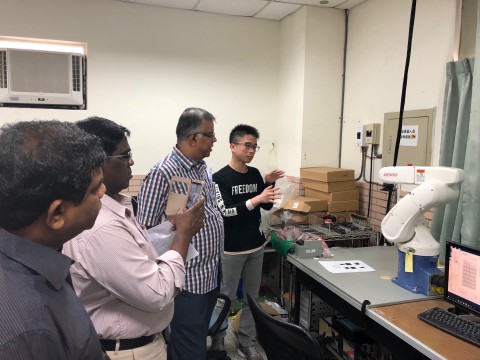

VLSI/CAD Laboratory (SF743)

Courses:

Digital Design, Logic Lab., Hardware Description Language, Introduction to Digital Chip Design,

Low-Power IC Design, Nanometer IC Design, Special Topics in Biomedical IC Design, Physics

Projects:

- Study of digitally controlled oscillator and all-digital spread-spectrum clock generator design (NSC 100-2218-E-030-001-, 2011/01/01 ~ 2011/10/31)

- Study of PVT tolerant all-digital clock generator for SoC applications (NSC 100-2221-E-030-012-,2011/08/01 ~ 2012/07/31)

- Study of an all-digital reference clock generator for WBAN applications (NSC 101-2221-E-030 -025-, 2012/08/01 ~ 2013/07/31)

- 智慧電子整合性人才培育計畫 - 生醫影像處理系統,教育部顧問室, 2011/09/01 ~ 2016/01/31

- Study of an all-digital UWB pulse generator for wireless biotelemetry applications (輔仁大學理工學院, 2014/02/01 ~ 2014/07/15)

- Study of an all-digital and high-resolution transmit beamformer for high-frequency ultrasonic imaging system applications (MOST 103-2221-E-030 -025 -, 2014/08/01 ~ 2015/07/31)

- Study of critical digital integrated circuit of positron emission tomography detector (MOST 104-2221-E-030-019-, 2015/08/01 ~ 2016/07/31)

- Study of an all-digital and high-resolution transmit beamformer for high-frequency ultrasonic imaging system applications (輔仁大學理工學院, 2015/10/01 ~ 2016/06/15)

- Study of digital multi-channel readout circuit for high-resolution Micro-PET detector applications (MOST 105-2221-E-030-017-, 2016/08/01 ~ 2017/07/31)

- Study of an all-digital and low-complexity dynamic focusing transmit beamformer for high-frequency ultrasonic imaging system applications (輔仁大學理工學院, 2016/11/01~2017/06/15)

- 應用於小型動物正子斷層造影檢測器之低操作環境變異敏感度數位積體電路設計 (輔仁大學, 2017/08/01 ~ 2018/07/31)

- 應用於高頻超音波系統之可設置性發射波束成像器研製 (輔仁大學理工學院, 2018/11/01 ~ 2019/06/15)

- Study of high-throughput and reconfigurable miniaturized TCSPC system chip design (MOST 108-2221-E-030-018-, 2019/08/01 ~ 2020/07/31)

- Design of plane-wave transceiver beamformer chip for multi-angle and high-resolution system applications (MOST 109-2221-E-030-016-MY2, 2020/08/01 ~ 2022/07/31)

- Study of transceiver chip for catheter-based ultrasound imaging system (MOST 111-2221-E-030-017-, 2022/08/01 ~ 2023/07/31)

- Study of TX/RX beamformer for portable 3D ultrafast ultrasound imaging system (NSTC 112-2221-E-030-016 -, 2023/08/01 ~ 2024/07/31)

Publications:

Journal Papers

- Duo Sheng, Hsin-Ting Lee, and Fu-Chi Huang,“All-digital transmit beamformer for portable high-frequency ultrasound imaging systems,”Review of Scientific Instruments, vol. 94, Mar. 2023. (SCI)

- Duo Sheng, Hsueh-Ru Lin, and Li Tai,“Low-Process–Voltage–Temperature-Sensitivity Multi-Stage Timing Monitor for System-on-Chip Applications,”Electronics, vol. 10, Jun. 2021. (SCI)

- Duo Sheng, Wei-Yen Chen, Hao-Ting Huang, and Li Tai,“Digitally controlled oscillator with high timing resolution and low complexity for clock generation,”Sensors, vol. 21, Feb. 2021. (SCI)

- Ching-Che Chung, Duo Sheng, and Ming-Hsuan Li,“Design of a human body channel communication transceiver using convolutional codes,”Microelectronics Journal, vol. 100, Jun. 2020. (SCI)

- Duo Sheng, Sheng-Min Chan, Chun-Wei Lin, and Chih-Chung Huang,“32-channel transmit beamformer with high timing resolution for high-frequency ultrasound imaging systems,”Review of Scientific Instruments, vol. 91, May 2020. (SCI)

- Duo Sheng, Jun-Wei Lin, Yi-Hsiang Wang and Chih-Chung Huang, “High-resolution all-digital transmit beamformer for high-frequency and wearable ultrasound imaging systems,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 2, pp. 492-502, Feb. 2020. (SCI)

- Duo Sheng, Chun-Wei Lin, Ying-Chen Shih, and Yun-An Yang,“Dual-cell structure digitally controlled oscillator with portability for clock generation applications,”Review of Scientific Instruments, vol. 90, May 2019. (SCI)

- Ching-Che Chung, Duo Sheng, Ming-Chieh Li, and Yi-Che Tsai, "A fast phase tracking reference-less all-digital CDR circuit for human body channel communications," Microelectronics Journal, vol. 84, pp.97-95, Feb. 2019. (SCI)

- Duo Sheng and Yu-Chan Hung,“Wide-range and high-resolution on-chip delay measurement circuit with low supply-voltage sensitivity for SoC applications,”Review of Scientific Instruments, vol. 87, Nov. 2016. (SCI)

- Duo Sheng and Min-Rong Hong,“A low-power all-digital on-chip CMOS oscillator for a wireless sensor node,”Sensors, vol. 16, Oct. 2016. (SCI)

- Ching-Che Chung, Duo Sheng, and Chang-Jun Li, “A wide-range low-cost all-digital duty-cycle corrector,”IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 11, pp. 2487-2496, Nov. 2015. (SCI)

- Ching-Che Chung, Duo Sheng, and Wei-Da Ho, “A low-cost low-power all-digital spread-spectrum clock generator,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 5, pp. 983-987, May. 2015. (SCI)

- Duo Sheng, Hsiu-Fan Lai, Sheng-Min Chan and Min-Rong Hong, “A high resolution on-chip delay sensor with low supply-voltage sensitivity for high-performance electronic systems,”Sensors, vol. 15, pp. 4408-4424, Feb. 2015. (SCI)

- Ching-Che Chung, Duo Sheng, and Sung-En Shen, “High-resolution all-digital duty-cycle corrector in 65-nm CMOS technology,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 5, pp. 1096-1105, May. 2014. (SCI)

- Duo Sheng, Ching-Che Chung, Hsiu-Fan Lai, and Shu-Syun Jhao,“High-resolution and all-digital on-chip delay measurement with low supply sensitivity for SoC applications,”IEICE Electronics Express (ELEX) , vol. 11, no. 3, Jan. 2014. (SCI)

- Ching-Che Chung, Duo Sheng, and Wei-Da Ho, “A counter-based all-digital spread-spectrum clock generator with high EMI reduction in 65nm CMOS,”IEICE Electronics Express (ELEX), vol. 10, no. 6, Mar. 2013. (SCI)

- Ching-Che Chung, Duo Sheng, and Ning-Mi Hsueh,“A high-performance wear-leveling algorithm for flash memory system,”IEICE Electronics Express (ELEX), vol. 9, no. 24, pp. 1874-1880, Dec. 2012. (SCI)

- Ching-Che Chung, Duo Sheng, Chia-Lin Chang, Wei-Da Ho, Yang-Di Lin, and Fang-Nien Lu,“An all-digital large-N audio frequency synthesizer for HDMI applications,”IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 59, no. 7, pp. 424-428, Jul. 2012. (SCI)

- Duo Sheng, Ching-Che Chung, Jhih-Ci Lan, and Hsiou-Fan Lai,“Monotonic and low-power digitally controlled oscillator with portability for SoC applications,”Electronics Letters, vol. 48, no. 6, pp. 321-323, Mar. 2012. (SCI)

- Ching-Che Chung, Duo Sheng, and Sung-En Shen,“A wide-range all-digital duty-cycle corrector with output clock phase alignment in 65nm CMOS technology,”IEICE Electronics Express (ELEX), vol. 8, no. 15, pp. 1245-1251, Aug. 2011. (SCI)

- Duo Sheng, Ching-Che Chung, and Chen-Yi Lee,“A Low-Power and Portable Spread Spectrum Clock Generator for SoC Applications,”IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 19, no. 6, pp. 1113-1117, Jun. 2011. (SCI)

- Ching-Che Chung, Duo Sheng, and Chia-Lin Chang,“A 600 kHz to 1.2 GHz all-digital delay-locked loop in 65nm CMOS technology,”IEICE Electronics Express (ELEX), vol. 8, no. 7, pp. 518-524, Apr. 2011. (SCI)

- Duo Sheng, Ching-Che Chung, and Chen-Yi Lee,“Wide Duty Cycle Range Synchronous Mirror Delay Designs,”Electronics Letters, vol. 46, no.5, pp. 338-340, Mar. 2010. (SCI)

- Duo Sheng, Ching-Che Chung, and Chen-Yi Lee,“Fast-Lock All-Digital DLL and Digitally-Controlled Phase Shifter for DDR Controller Applications,”IEICE Electronics Express, vol. 7, no.9, pp. 634-639, May 2010. (SCI)

- Duo Sheng, Ching-Che Chung, and Chen-Yi Lee, “An Ultra-Low-Power and Portable Digitally Controlled Oscillator for SoC Applications,” IEEE Trans. Circuits and Syst. II, Exp. Briefs, vol. 54, no. 11, pp. 954-958, Nov. 2007. (SCI)

- Jinn-Shyan Wang, Po-Hui Yang, and Duo Sheng, “Design of a 3-V 300-MHz low-power 8-b×8-b pipelined multiplier using pulse-triggered TSPC flip-flops,”IEEE J. Solid-State Circuits, vol. 35, no. 4, pp. 583–592, Apr. 2000. (SCI)

- Duo Sheng, Ying-Chi Chiu, Yun-Quan Li, You-Ning Lo, Chao-Kai Pai, and Ten-Ling Wang,“A Digital Receive Beamforming IC for High-Frequency Ultrasound Imaging System,”IEEE International Conference on ASIC (ASICON), Oct. 2023.

- Duo Sheng, Chih-Hao Liu, Sih-Ying Chen, Bin-Yang Song, Ying-Chi Chiu, and Ming-Han Cai,“DLL-based transmit beamforming IC for high-frequency ultrasound medical imaging system,”IEEE International Conference on Consumer Electronics-Taiwan (ICCE-TW), Sep. 2021.

- Duo Sheng, Wei-Yen Chen, Yu-Hsiang Chang, and Hao-Ting Huang, "High-Timing-Resolution and Low-Complexity Cell-Based Digitally Controlled Oscillator," IEEE International Conference on Consumer Electronics-Taiwan (ICCE-TW), Sep. 2020.

- Duo Sheng, Chia-Lin Wu, Yu-Chan Hung, and Yi-Shang Wang, “All-digital and low-power reference clock generator for biotelemetry applications,” International Technical Conference on Circuits/Systems, Computers and Communications (ITC-CSCC), Jul. 2016.

- Duo Sheng, Chih-Chung Huang, Zong-Ru Yang, and Yi-Shang Wang,“An all-digital and high-resolution transmit beamforming ASIC for high-frequency and portable ultrasonic imaging systems,”IEEE International Ultrasonics Symposium, Oct. 2015.

- Duo Sheng, Ching-Che Chung, Chia-Lin Wu, Sheng-Min Chan, and Min-Rong Hong, “An all-digital and wide-range reference clock generator for biotelemetry applications,”International Conference on Electronics and Software Science (ICESS), Jul. 2015.

- Ching-Che Chung, Duo Sheng, and Chen-Han Chen,“An all-digital phase-locked loop compiler with liberty timing files,”IEEE International Symposium on VLSI Design, Automation, and Test (VLSI-DAT), Apr. 2014.

- Duo Sheng, Ching-Che Chung, Chih-Chung Huang, and Jia-Wei Jian,“A high-resolution and one-cycle conversion time-to-digital converter architecture for PET image applications,”35th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Jul. 2013.

- Duo Sheng and Zong-Ru Yang, “A low-energy and all-digital pulse generator of IR-UWB transmitter for capsule endoscope,”35th Annual International Conference of the IEEE Engineering in Medicine and Biology Society (EMBC), Jul. 2013.

- Ching-Che Chung, Duo Sheng, and Wei-Siang Su,“A 0.5V/1.0V fast lock-in ADPLL for DVFS battery-powered devices,”IEEE International Symposium on VLSI Design, Automation, and Test (VLSI-DAT), Apr. 2013.

- Duo Sheng, Ching-Che Chung, and Jhih-Ci Lan,“A monotonic and low-power digitally controlled oscillator using standard cells for SoC applications, IEEE 4th Asia Symposium on Quality Electronic Design (ASQED), Jul. 2012.

- Ching-Che Chung, Duo Sheng, and Yang-Di Lin, “An all-digital clock and data recovery circuit for spread spectrum clocking applications in 65nm CMOS technology,”IEEE 4thAsia Symposium on Quality Electronic Design (ASQED), Jul. 2012.

- Ching-Che Chung, Duo Sheng, and Wei-Da Ho,“A low-power and small-area all-digital spread-spectrum clock generator in 65nm CMOS technology,” IEEE International Symposium on VLSI Design, Automation, and Test (VLSI-DAT), Apr. 2012

- Duo Sheng, and Jhih-Ci Lan,“A Monotonic and Low-Power Digitally Controlled Oscillator with Portability for SoC Applications,”54th IEEE Midwest Symposium on Circuits and Systems (MWSCAS), Aug. 2011.

- Duo Sheng, Ching-Che Chung, and Chen-Yi Lee, “An All Digital Spread Spectrum Clock Generator with Programmable Spread Ratio for SoC Applications,”IEEE Asia Pacific Conf. on Circuits and Systems (APCCAS), Nov. 2008, pp. 850–853.

- Duo Sheng, Ching-Che Chung, and Chen-Yi Lee, “An All-Digital Phase-Locked Loop with High-Resolution for SoC Applications,” IEEE International Symposium on VLSI Design, Automation, and Test (VLSI-DAT),, Apr. 2006, pp. 207-210.

- Duo Sheng, Ching-Che Chung, and Chen-Yi Lee,“A Fast-Lock-In ADPLL with High-Resolution and Low-Power DCO for SoC Applications,”IEEE Asia Pacific Conf. on Circuits and Systems (APCCAS), Dec. 2006, pp. 105–108.

- Jinn-Shyan Wang, Pei-Lung Lin, Wern-Ho Sheen, Duo Sheng, and Yu-Ming Huang, “A compact adaptive equalizer IC for HIPERLAN system,”IEEE International Symposium on Circuits and Systems (ISCAS), pp. 265-268, May 2000.

Patents:

- Duo Sheng, Min Nan Yen, Ken Liou, “Re-programmable logic array,” US Patent No. 6693453, 2004.

- Min Nan Yen and Duo Sheng, “Memory device having built-in error-correction capabilities,” US Patent No. 7079430, 2006.

- Min Nan Yen, Duo Sheng, Shou-Chang Tsai, Koug Mou Liou “Digital phase-locked loop compiler,” US Patent No. 7145975, 2006.

- 嚴敏男,盛鐸,蔡壽昌,劉康懋,“數位式鎖相迴路”,中華民國專利發明第I245491號,94年。

- 嚴敏男,盛鐸,“具有內建錯誤糾正能力之記憶體元件”,中華民國專利發明第I301975號,97年。

Services:

Paper Reviewer

- IEEE Transactions on Circuits and Systems I (TCAS-I)

- IEEE Transactions on Circuits and Systems II (TCAS-II)

- IEEE Transactions on Very Large Scale Integration (VLSI) Systems

- IEEE Transactions on Biomedical Circuits and Systems

- IEEE Transactions on Instrumentation & Measurement

- Sensors

- Review of Scientific Instruments

- Microelectronics Journal

- IEICE Electronics Express (ELEX)

- Integration the VLSI Journal

- Electronics

- IEEE Symposium on VLSI Circuit

- IEEE International Symposium on Circuits & Systems

- The 31st VLSI Design/CAD Symposium (Session Chair)

- The 30th ~ 34th VLSI Design/CAD Symposium (TPC)

- The 6th International Symposium on Next-Generation Electronics (Session Chair)

- Symposium on Engineering, Medicine, and Biology Applications (Session Chair)